Компания Samsung объявила о создании экспериментальной 256-мегабитной матрицы памяти SRAM с использованием 3-нм технологического процесса и совершенного нового MBCFET-транзистора. Образец позволил нам подтвердить характеристики будущего технического процесса. Таким образом, Samsung перешла от теории к практике, и можно ожидать, что в следующем году она запустит 3-нм производство полупроводников.

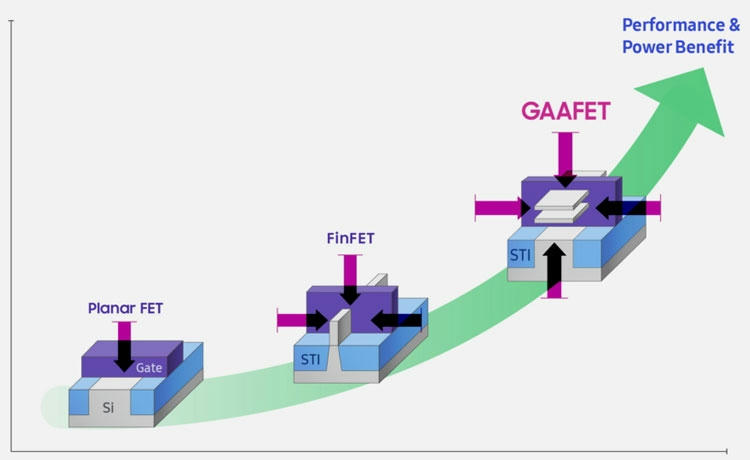

Эволюция транзисторов. Источник изображения: Samsung

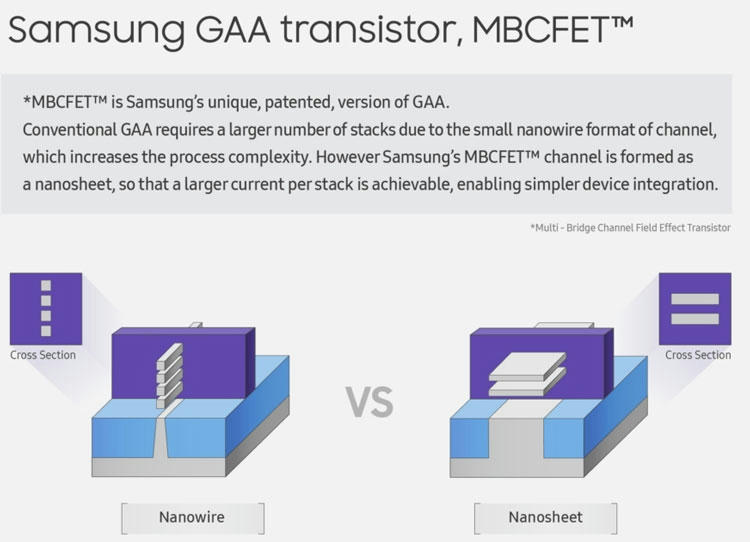

Следует отметить, что аббревиатура MBCFET (multi-bridge channel FET) в названии нового типа транзисторов является зарегистрированной торговой маркой Samsung. В широком смысле это так называемые ГААФЕТ-транзисторы с кольцевым или всеобъемлющим затвором, когда канал или несколько каналов транзистора окружены затвором со всех четырех сторон.

Эта концепция была введена еще в 1988 году и хорошо изучена теоретически, но повод перейти на эту структуру появился только сейчас, так как классические транзисторы FinFET с вертикальными ребрами перестают нормально работать при технологических стандартах менее 5 нм. В случае дальнейшего повышения производительности и снижения потребления при одновременном уменьшении физических размеров транзисторов (в процессе снижения технологических норм) становится сложнее управлять транзисторными каналами. Поэтому увеличение площади контакта между затвором и каналом за счет полного покрытия канала является простым выходом из сложившейся ситуации, что, что очень важно, позволяет производить новые транзисторы на том же оборудовании.

Источник изображения: Samsung

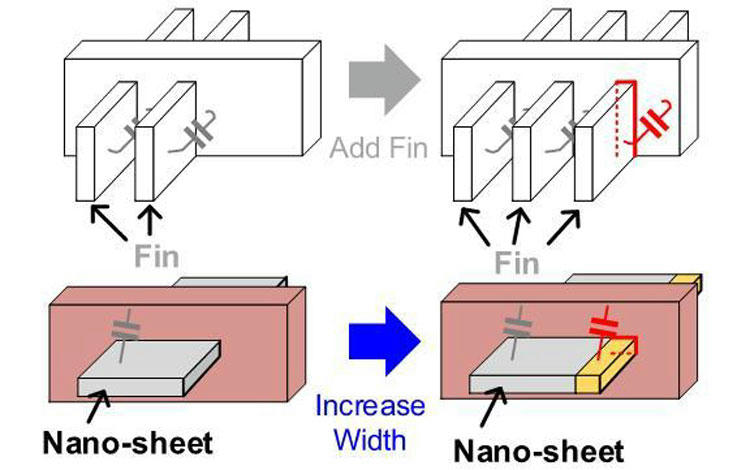

Добавим, что важным нововведением в производстве микросхем на основе MBCFET-транзисторов (GAAFET) станет возможность задавать ширину наностажных каналов, а также их количество в каждом транзисторе, для каждого отдельного случая. Например, для более производительной логики ширина нанопокрытий может быть увеличена, а для блоков с низким потреблением-уменьшена.

Более того, становится возможным проектировать настолько гибко, что даже в одной шестистранной элементарной ячейке SRAM некоторые транзисторы могут быть созданы с широкими наностран-каналами, а некоторые — с узкими. Именно это Samsung продемонстрировала при создании экспериментального 256-Мбит-3-нм массива SRAM. Измерения показали, что переключение на ячейку со смешанными транзисторами на плоском месте снижает напряжение записи на 256 мВ.

Контролировать ширину каналов нанопроволоки проще, чем добавлять новые ребра в транзисторах FinFET. Источник изображения: Samsung

Наконец, компания доказала свою способность достигать новых уровней производительности и эффективности. Так, по сравнению с 7-нм техпроцессом 7LPP, быстродействие 3-нм MBCFET транзисторов возросло до 30 % (при том же уровне потребления и сложности), а при работе на тех же частотах и той же сложности потребление снизилось до 50 %. Увеличение плотности транзисторов в смешанной схеме (SRAM plus logic) составило до 80 %.