Ситуація з технологією Resizable BAR (базові Адресні регістри), яка є частиною специфікацій інтерфейсу PCI Express, починаючи з версії 2.0, І є основою для AMD Smart Access Memory (SAM), продовжує прояснюватися. Нещодавно ми писали, що SAM працювала над купою процесорів Radeon RX 6000 і Intel, а тепер стали відомі деталі старіших процесорів AMD.

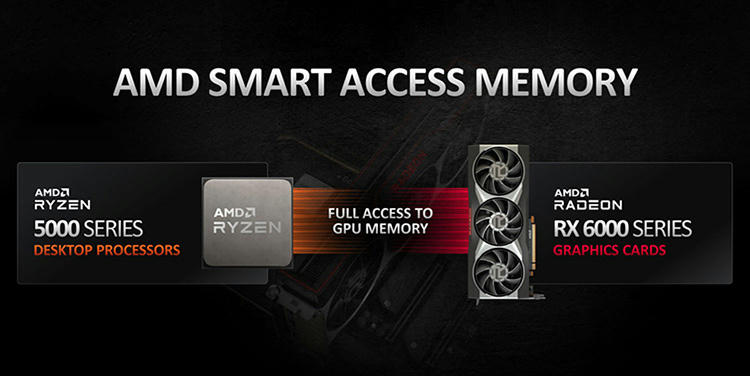

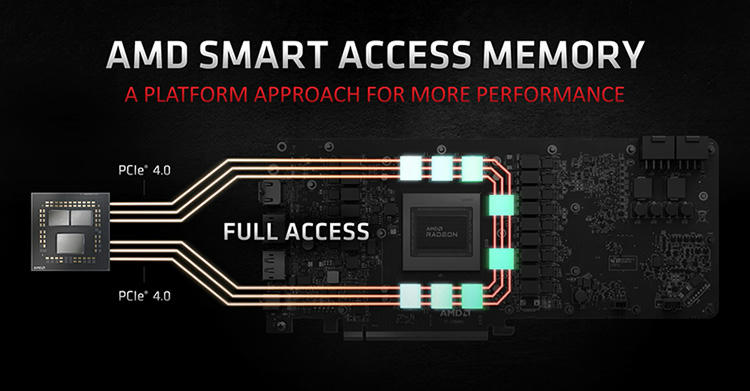

Згадай: компанія AMD представила технологію SAM під час анонсу відеокарт Radeon RX 6000 і спочатку анонсувала її тільки для процесорів Ryzen 5000. У той час як в звичайних ПК на базі Windows процесори можуть одночасно отримувати доступ тільки до частини графічної пам’яті розміром до 256 Мбайт, дана технологія дозволяє розширити канал передачі даних, дозволяючи процесору відразу ж використовувати весь масив відеопам’яті і усунути потенційні вузькі місця, домагаючись підвищеної продуктивності в деяких іграх.

Здається, не випадково AMD почав говорити про підтримку SAM тільки з запуском архітектури Zen 3-справа в тому, що процесори AMD Ryzen 3000 сімейства Matisse на базі Zen 2, а також старіші рішення на базі Zen+ і Zen не підтримують цю функцію. Виявилося, що шина PCI-Express процесорів Ryzen 5000 Vermeer включає в себе функціональність фізичного рівня PCIe під назвою full rate _pdep_u32 / 64, яка необхідна для Resizable BAR.

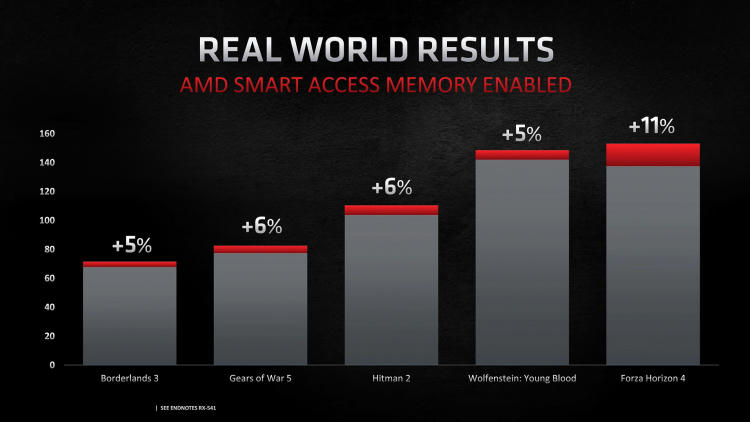

Офіційні дані про приріст продуктивності SAM на платформах AMD Ryzen 5000 і Radeon 6000

Більш цікавим є те, що процесори Intel підтримують цю функціональність ще з 4-го покоління Core від Haswell, яке додало 20-діапазонну шину PCI-Express Gen 3.0. Це означає, що кожен процесор Intel, що випускається з 2014 року, технічно здатний підтримувати Resizable BAR, і питання тільки для виробників материнських плат, які випускають оновлення мікропрограмного забезпечення UEFI для своєї продукції (тобто. Чіпсетів Intel 8 — ї і пізніших серій).

AMD широко рекламує SAM як засіб підвищення продуктивності на 1-2% для відеокарт Radeon RX серії 6800. Оскільки це є частиною специфікацій PCI Express, NVIDIA також планує додати підтримку для деяких своїх графічних процесорів.